เกิดอะไรขึ้นที่อินเทล ตอนที่ 2: ทำไมอินเทลไป 10 นาโนเมตรยาก แต่ TSMC ทำได้

ต่อเนื่องจากตอนที่แล้ว ปัญหาที่ทุกคนสงสัยคงเป็นว่าทำไมอินเทลติดหล่ม 14 นาโนเมตรอยู่หลายปี มาถึงวันนี้ (ต้นปี 2021) ยังก้าวไม่ถึง 10 นาโนเมตรได้สมบูรณ์ 100% เลยด้วยซ้ำ แถมแผนการผลิตชิป 7 นาโนเมตรก็ล่าช้ากว่ากำหนด

ในทางกลับกัน คู่แข่งสายโรงงานผลิตชิปทั้ง TSMC และซัมซุง สามารถผลิตชิประดับ 7 นาโนเมตรได้ก่อนแล้วหลายปี (Radeon VII ที่ผลิตโดย TSMC 7nm ออกต้นปี 2019) ตอนนี้ยังเริ่มผลิตชิปที่ 5 นาโนเมตรได้แล้ว

อะไรคือความแตกต่างระหว่างอินเทลกับคู่แข่ง คำตอบของคำถามนี้ต้องย้อนไปดูพัฒนาการของอุตสาหกรรมเซมิคอนดักเตอร์กันก่อน

อุตสาหกรรมเซมิคอนดักเตอร์ มีทุกอย่างในตัว vs รับจ้างผลิตอย่างเดียว

ในอดีต บริษัทผลิตชิปชั้นนำมักมีโรงงานผลิตชิปของตัวเอง เพื่อให้ควบคุมปริมาณการผลิตและต้นทุนได้ การมีเทคโนโลยีฝั่งการผลิตของตัวเองถือเป็นแต้มต่อที่สำคัญในการแข่งขัน เพราะเทคโนโลยีการออกแบบชิป (design) นั้นผูกพันกับการผลิต (manufacturing) อย่างแนบแน่น บริษัทกลุ่มนี้เรียกว่า integrated device manufacturer (IDM) ทุกอย่าง integrated เข้าด้วยกันตั้งแต่ต้นน้ำยันปลายน้ำ

อินเทลถือเป็นเรือธงของบริษัทที่ใช้แนวคิด "ออกแบบ-ผลิต" ทำทุกอย่างเอง ตั้งแต่สถาปัตยกรรม (x86) ชุดคำสั่ง และการผลิต แนวทาง vertical integration นี้ถือเป็นจุดแข็งของอินเทล และส่งผลให้อินเทลกลายเป็นราชาแห่งโลกซีพียูมายาวนาน

แต่นอกจากอินเทล ยังมีบริษัทอื่นๆ อีกมากที่เคยใช้แนวทางนี้ เช่น คู่แข่งหน้าเดิมๆ AMD, Texas Instruments, Motorola (ที่ทำ PowerPC), ยักษ์ใหญ่ IBM (จำ Cell ซีพียูพลิกโลกกันได้ใช่ไหมครับ) หรือบริษัทฝั่งญี่ปุ่นอย่าง Toshiba, Hitachi, NEC ล้วนแต่มีโรงงานผลิตชิปกันมาก่อนทั้งนั้น

ในอดีต บริษัทเหล่านี้ถือเป็นผู้ผลิตชิป "ชั้นนำ" ที่มีดีไซน์ของตัวเอง ผลิตเอง ขายเอง สร้างมูลค่าเพิ่มได้มากกว่ามาก ซึ่งมักเป็นบริษัทฝั่งตะวันตกหรือญี่ปุ่น บริษัทบางแห่งอาจเลือกเปิดรับออเดอร์จ้างผลิตจากบริษัทอื่นบ้าง (เช่น ชิปของ Cyrix ผลิตที่โรงงานของ TI และ IBM)

ในอีกด้าน เรามีบริษัทผลิตชิป "ชั้นรอง" ที่ไม่มีดีไซน์ของตัวเอง จึงต้องรับงานจ้างผลิตชิปแบบพื้นๆ เทคโนโลยีไม่สูงมาก (เช่น ชิปที่ตกรุ่นไปแล้ว ใช้กระบวนการผลิตที่ไม่ทันสมัยมาก หรือชิปสำหรับอุปกรณ์ประเภทอื่นๆ ที่ไม่ต้องล้ำเท่าพีซี) โมเดลรับจ้างผลิตมีอัตรากำไรต่ำกว่า บริษัทกลุ่มนี้มักอยู่ในประเทศกำลังพัฒนา (ในสมัยนั้น) เช่น ไต้หวัน (TSMC, UMC, Vanguard), เกาหลีใต้ (Dongbu), สิงคโปร์ (Chatered), จีน (SMIC), อิสราเอล (Tower) เป็นต้น

บริษัทกลุ่มที่สองมีชื่อเรียกรวมๆ ว่า Pure-play รับจ้างผลิตอย่างเดียว ไม่ออกแบบชิปเองเลย ชิปที่บริษัทกลุ่มนี้รับจ้างผลิต มักเป็นชิปที่ไม่ต้องเป็นเทคโนโลยีล้ำหน้าที่สุด (อย่างที่ซีพียูคอมพิวเตอร์ต้องเป็น) เช่น อุปกรณ์สื่อสาร อุปกรณ์อุตสาหกรรม หน่วยความจำ เป็นต้น

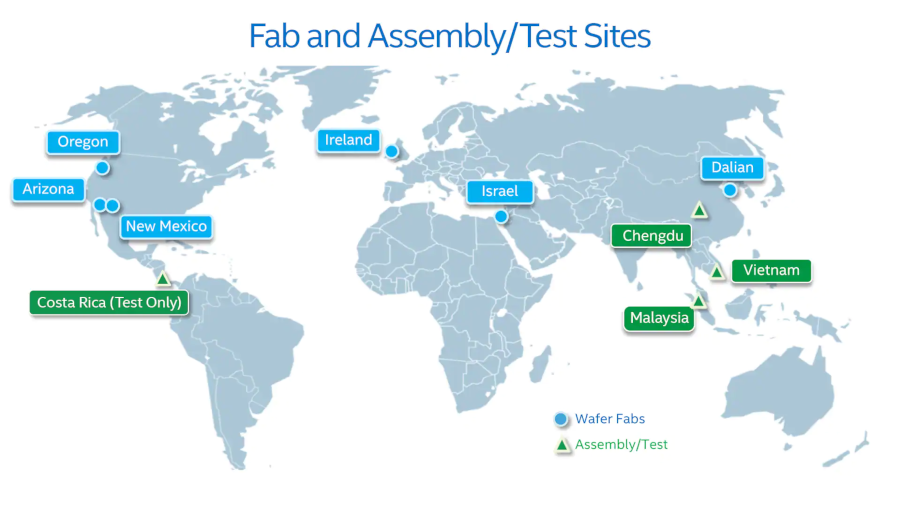

แผนที่แสดงโรงงานผลิตชิปทั่วโลกของอินเทล ภาพจาก Intel

กฎข้อที่สองของมัวร์ ราคาโรงงานผลิตชิปจะแพงขึ้นเรื่อยๆ

คนในแวดวงไอทีคงคุ้นเคยกับ "กฎของมัวร์" (Moore's law) ของกอร์ดอน มัวร์ ผู้ร่วมก่อตั้งบริษัทอินเทล ที่สังเกตพบว่าปริมาณทรานซิสเตอร์ในชิปจะเพิ่มขึ้น 2 เท่าทุก 2 ปี กฎข้อนี้กลายเป็นสิ่งสำคัญที่ขับเคลื่อนวงการเซมิคอนดักเตอร์มาตลอด

แต่จริงๆ แล้ว กอร์ดอน มัวร์ยังมีกฎอีกข้อ ที่เรียกกันเล่นๆ ว่ากฎข้อที่สองของมัวร์ (Moore's second law) ที่บอกว่า "ต้นทุนของโรงงานผลิตชิปจะเพิ่มขึ้น 2 เท่าทุก 4 ปี" (กฎข้อนี้มีอีกชื่อว่า Rock's Law เรียกตาม Arthur Rock หนึ่งในนักลงทุนคนแรกของอินเทล ที่สังเกตพบเรื่องนี้เช่นกัน)

กฎของมัวร์ทั้งสองข้อถือเป็นด้านกลับซึ่งกันและกัน ในทางหนึ่ง จำนวนทรานซิสเตอร์ในชิปจะเพิ่มขึ้นเรื่อยๆ ทำให้ความหนาแน่นสูงขึ้น ตัวทรานซิสเตอร์จึงต้องมีขนาดเล็กลง

แต่ในอีกทางหนึ่ง ขนาดทรานซิสเตอร์ที่เล็กลง ทำให้ต้นทุนในการผลิตชิปเพิ่มสูงขึ้นเช่นกัน เพราะต้องใช้เครื่องจักรและกลไกการผลิตที่ซับซ้อนมากขึ้น มีปัญหาเรื่องอัตราผลิตสำเร็จ (yield) เพิ่มขึ้น

ถ้าลองเทียบตัวเลขแบบหยาบๆ โรงงานของอินเทล Fab 22 ในแอริโซนา ที่เริ่มก่อสร้างในปี 2000 (ผลิตชิป 22nm ภายหลังอัพเกรดเป็น 14nm) ใช้เงินลงทุน 2 พันล้านดอลลาร์ (อ้างอิงจากเว็บอินเทล) ส่วนโรงงานใหม่ล่าสุด Fab 42 ในเมืองเดียวกัน ผลิตชิป 10nm/7nm สร้างเสร็จในปี 2020 ใช้เงินลงทุนถึง 7 พันล้านดอลลาร์ (อ้างอิงจาก Tom's Hardware) เรียกว่าเพิ่มขึ้นอย่างน้อยๆ 3 เท่า

คลิปวิดีโอของอินเทลเอง พาทัวร์ Fab 42

อุตสาหกรรมเซมิคอนดักเตอร์ในยุคเปลี่ยนผ่านสู่ Fabless

การที่โรงงานผลิตชิปมีราคาแพงขึ้นเรื่อยๆ ย่อมส่งผลให้มีบริษัทชิปที่ไปต่อไม่ไหว กรณีของอินเทลที่เป็นเบอร์หนึ่งของวงการมายาวนาน มีกำไรอู้ฟู่เสมอมา ย่อมไม่มีปัญหานี้ แต่คู่แข่งระดับรองๆ ที่ไม่รวยแบบอินเทล ก็เริ่มไม่สามารถลงทุนโรงงานในระดับหลายพันล้านดอลลาร์อีกแล้ว

AMD คือตัวอย่างที่ดีที่สุดของการเปลี่ยนแปลงนี้ ในฐานะเบอร์สองที่ตามหลังอินเทลแบบห่างมากๆ และเคยมีสถานการณ์การเงินย่ำแย่อยู่พักใหญ่ๆ AMD จึงไม่สามารถไปต่อในโมเดล vertical integration ได้อีกแล้ว ในช่วงปี 2008-2009 เราจึงเห็น AMD แยกบริษัท GlobalFoundries ออกมาเป็นอิสระ ทำหน้าที่รับจ้างผลิตชิปอย่างเดียว (pure-play) ในขณะที่ AMD กลายเป็นบริษัทออกแบบชิปอย่างเดียว ไม่มีโรงงานของตัวเอง (fabless)

ยุทธศาสตร์การแยกบริษัททำให้ AMD เป็นอิสระและคล่องตัวขึ้นมาก สามารถไปจ้างโรงงานที่ไหนผลิตชิปให้ก็ได้ (ซึ่งในระยะเวลาต่อมา เราเห็น AMD ไปจ้าง TSMC) ในขณะเดียวกัน GlobalFoundries ก็มีความอิสระขึ้นเช่นกัน เปลี่ยนสถานะเป็นโรงงานรับจ้างผลิตอย่างเดียว และภายหลัง AMD ก็ขายหุ้นทั้งหมดใน GlobalFoundries ด้วย ทำให้ GlobalFoundries แยกขาดจาก AMD อย่างสมบูรณ์

อีกบริษัทที่เดินตามแนวทางนี้คือ IBM ซึ่งในอดีตเป็น vertical integration แบบสุดๆ เช่นกัน ตั้งแต่เป็นเจ้าของสถาปัตยกรรมเอง (Power) ไปจนถึงเป็นเจ้าของโรงงานเอง แต่พอโมเดลนี้เดินต่อไปไม่ได้ IBM ก็ขายโรงงานผลิตชิปให้ GlobalFoundries ในปี 2014 (แถมเป็นการขายแบบขาดทุนด้วย) หลุดพ้นจากธุรกิจเซมิคอนดักเตอร์เช่นกัน

ภาพโรงงานผลิตชิปของ IBM เมื่อปี 2005 ที่ตอนนั้นถูกยกย่องว่าก้าวหน้าที่สุดในโลก - IBM

ในอีกทาง อุตสาหกรรมรับจ้างผลิตชิปแบบ pure-play ก็เริ่มค้นพบฐานลูกค้าใหม่ๆ คือ บริษัทออกแบบชิปรุ่นใหม่ที่ทำงานออกแบบชิปอย่างเดียว ไม่มีโรงงานเป็นของตัวเอง (fabless)

ตัวอย่างบริษัท fabless ที่โดดเด่นที่สุดในยุคแรกคือ NVIDIA ที่ค้นพบตลาดเกิดใหม่ (จีพียู) ทำให้ไม่ต้องไปแข่งขันโดยตรงกับยักษ์ใหญ่แบบอินเทล

NVIDIA เริ่มต้นจากการเป็นสตาร์ตอัพ (ก่อตั้งในปี 1993) ย่อมไม่มีเงินไปลงทุนสร้างโรงงานเองแน่ๆ บริษัทมีดีอย่างเดียวคือดีไซน์ จึงต้องใช้วิธีจ้างผลิต โดย GeForce 256 รุ่นแรกที่ออกในปี 1999 เลือกใช้โรงงานของ TSMC ที่ตอนนั้นใช้กระบวนการผลิต 220 นาโนเมตร ส่วนบริษัทผลิตชิปในรุ่นหลังที่ใช้โมเดลนี้ โดดเด่นที่สุดย่อมหนีไม่พ้น Apple กับชิปตระกูล A Series ของ iPhone นั่นเอง

การจับคู่ระหว่างบริษัท pure-play และ fabless กลับกลายเป็นส่วนผสมที่ลงตัว สมประโยชน์กันทั้งสองฝ่าย บริษัทออกแบบ (fabless) ไม่ต้องลงทุนเยอะ ในขณะที่บริษัทผลิต (pure-play) รวมออเดอร์เยอะพอคุ้มค่าแก่การสร้างโรงงานราคาแพง ทำให้พันธมิตร pure-play + fabless สามารถต่อสู้กับ IDM แบบดั้งเดิมได้

ภาพจาก Stratechery

TSMC ตำนานแห่งไต้หวัน เบอร์หนึ่งของโลก Pure-play

หาก NVIDIA เป็นตัวอย่างที่โดดเด่นของบริษัท fabless แท้ๆ ฝั่งของบริษัท pure-play ที่โดดเด่นที่สุดย่อมหนีไม่พ้น TSMC หรือชื่อเต็ม Taiwan Semiconductor Manufacturing Company

TSMC ก่อตั้งในปี 1987 โดย Morris Chang ชาวไต้หวันที่เคยทำงานเป็นผู้บริหารของ Texas Instruments นานถึง 25 ปี แล้วจึงกลับไต้หวันมาก่อตั้ง TSMC ถือเป็นต้นแบบของบริษัทรับจ้างผลิตชิป pure-play ยุคแรก

TSMC เติบโตขึ้นมาพร้อมๆ กับอุตสาหกรรมเซมิคอนดักเตอร์ของไต้หวัน (ซึ่งปัจจุบันเป็นศูนย์กลางด้านเซมิคอนดักเตอร์ของโลกไปแล้ว) บริษัทใช้เวลาเพียง 10 ปี ขยายตัวอย่างก้าวกระโดด จนกลายเป็นบริษัทไต้หวันรายแรกที่ขายหุ้น IPO ในตลาดหลักทรัพย์นิวยอร์กได้สำเร็จ

ลูกค้าของ TSMC เป็นบริษัทผลิตชิปจากทั่วโลก ที่เคลื่อนย้ายตามกระแส offshoring แสวงหาโรงงานผลิตที่ต้นทุนถูกลง ข้อมูลเก่าที่สุดที่ผมสามารถหาได้คือ รายงานประจำปีของ TSMC ในปี 1994 ที่ระบุว่าสัดส่วนลูกค้า 57% มาจากสหรัฐอเมริกา กลุ่มสินค้าที่รับจ้างผลิตมีตั้งแต่ SRAM, DRAM, CMOS, ASIC เป็นต้น

ในทศวรรษ 2000 บริษัทรับจ้างผลิตได้ลูกค้ากลุ่มใหม่ๆ อย่างจีพียูของ NVIDIA แต่พอเข้าทศวรรษ 2010s บริษัทก็เจอตลาดที่ใหญ่กว่ามากๆ นั่นคือชิปสำหรับสมาร์ทโฟน

บริษัทที่ผลิตชิปเกี่ยวกับการสื่อสาร ไม่ว่าจะเป็น Broadcom, Qualcomm, Marvell, MediaTek, Apple ล้วนแต่เป็นลูกค้าของ TSMC ด้วยเหตุผลข้างต้นว่า โรงงานผลิตชิปมีราคาแพงขึ้นเรื่อยๆ การทุ่มเงินผลิตย่อมไม่คุ้มค่า การออกแบบชิปเอง เป็นบริษัทแบบ fabless แล้วมาจ้างบริษัทแบบ TSMC ผลิตให้ ย่อมเป็นทางเลือกที่ดีกว่ามากในแง่ต้นทุน

โครงสร้างรายได้ของ TSMC ปี 2005 - TSMC

โครงสร้างรายได้ของ TSMC ปี 2010 - TSMC

โครงสร้างรายได้ของ TSMC ปี 2015 - TSMC

จะเห็นว่า TSMC ได้ลูกค้าทั้งกลุ่มซีพียู จีพียู และสมาร์ทโฟน ทั้งหมดเป็นตลาดที่เติบโตอย่างมากในรอบ 2 ทศวรรษที่ผ่านมา ทำให้เกิดวัฏจักรขาขึ้น (virtuous cycle) ทำให้บริษัทมีรายได้มั่นคง สามารถนำเงินไปลงทุนสร้างโรงงานใหม่ที่มีเทคโนโลยีการผลิตดีขึ้น เพื่อรับงานผลิตชิปรุ่นใหม่ๆ ที่ก้าวหน้าขึ้น มีรายได้เพิ่มเข้ามาอีกไปเรื่อยๆ

วัฏจักรความรุ่งเรืองของ TSMC ส่งผลให้เทคโนโลยีการผลิตของบริษัทก้าวหน้าอย่างรวดเร็ว บนเว็บไซต์ของ TSMC ประกาศ "วิสัยทัศน์" ของบริษัทไว้ 3 ข้อ โดยข้อแรกสุดคือบอกว่า ต้องการเป็นผู้นำด้านเทคโนโลยี ที่สามารถแข่งขันกับบริษัท IDM ชั้นแนวหน้าได้ (be a technology leader, competitive with the leading IDMs)

มาถึงตอนนี้แล้วคงไม่ต้องเดาว่า "บริษัท IDM ชั้นแนวหน้า" ที่ว่านี้คือใคร

เป้าหมายของ TSMC บริษัทที่มีเทคโนโลยีการผลิตชิปก้าวหน้าที่สุดในโลก... อินเทล

TSMC แซงหน้าอินเทลได้อย่างไร

อินเทลและ TSMC ถือเป็นตัวอย่างของโมเดลบริษัทผลิตชิปที่แตกต่างกันอย่างสิ้นเชิง โดยอินเทลเป็นเบอร์หนึ่งของบริษัท IDM ที่มีครบทุกอย่างมายาวนาน ในขณะที่ผู้ท้าชิง TSMC อาศัย economy of scale รวมพลังของบริษัท fabless จำนวนมาก ก้าวขึ้นมาท้าทายอินเทลได้สำเร็จ

หมายเหตุ: อีกบริษัทที่ขึ้นมาท้าทายอินเทลได้ในเรื่องเทคโนโลยีการผลิตคือ Samsung Semiconductor เพียงแต่โมเดลของซัมซุงต่างไป เพราะมีผลิตภัณฑ์ชิปของตัวเองด้วย (เช่น แรม สตอเรจ เซ็นเซอร์กล้อง ซีพียู) ต้องถือว่าซัมซุงเป็นบริษัท IDM ที่เปิดรับออเดอร์จากบริษัทอื่นด้วย ในขณะที่อินเทลเป็น IDM แบบไม่รับจ้างคนอื่นเลย กรณีของซัมซุงจะไม่กล่าวถึงในบทความนี้มากนัก

หากดูข้อมูลย้อนหลัง อินเทลสามารถออกชิป 14 นาโนเมตรได้ในปี 2014 (Broadwell) แต่ในปี 2014 ปีเดียวกัน TSMC ยังทำชิปได้เล็กที่สุดที่ 20 นาโนเมตรเท่านั้น (ข้อมูลจาก TSMC Q4/2014)

ในปี 2015 TSMC ก็ยังทำได้ที่ 16 นาโนเมตร และเริ่มผลิต 10 นาโนเมตรเป็นจำนวนมากได้จริงๆ ในปี 2017

หากดูแผนการเดิมของอินเทลที่ตั้งเป้า 10 นาโนเมตรในปี 2016 จะเห็นว่าตอนนั้นอินเทลยังนำหน้า TSMC อยู่พอสมควร (นี่ยังไม่นับเรื่องปัจจัย "นาโนเมตร" ของแต่ละบริษัทไม่เท่ากัน ซึ่งจะกล่าวต่อไป) นั่นแปลว่าถ้าอินเทลไม่พลาดเอง TSMC คงไม่สามารถเอาชนะอินเทลได้ง่ายนัก

คำถามคือ ในช่วงปี 2014-2015 อินเทลนำหน้าไปไกลกว่า TSMC ไปนานพอสมควร ทำไมอินเทลถึงไปต่อไม่ได้ และติดขัดอยู่หลายปีจนถูกแซง

ก่อนจะตอบคำถามนี้ ต้องเข้าใจคำนิยามเรื่อง "นาโนเมตร" กันก่อน

ภาพจาก Intel

นาโนเมตรของเราไม่เท่ากัน

ตัวเลขกระบวนการผลิตที่เรียกกันตามตัวเลข "นาโนเมตร" เป็นสิ่งที่อยู่คู่กับวงการเซมิคอนดักเตอร์มานาน แต่ในรอบทศวรรษหลัง เมื่อชิปมีความซับซ้อนมากขึ้น แพ็กเกจชิปหนึ่งตัวประกอบด้วยชิปหลากหลายประเภทที่ทำหน้าที่คนละอย่าง ทรานซิสเตอร์ในชิปตัวเดียวกันกลับใช้กระบวนการผลิตไม่เท่ากัน การเรียกว่าชิปตัวนี้ผลิตที่กระบวนการขนาดไหน เริ่มกลายเป็นสิ่งที่ยากขึ้น

"นาโนเมตร" จึงกลายเป็นศัพท์ทางการตลาด มากกว่าคำนิยามในทางเทคนิคจริงๆ

ตัวเลขอื่นที่อาจเหมาะสมกว่าในการวัดระดับเทคโนโลยีการผลิตชิป จึงเป็นความหนาแน่น (transistor density) ที่วัดเป็นจำนวนชิปต่อตารางมิลลิเมตร (transistors/mm2)

หากดูข้อมูลเปรียบเทียบในแหล่งที่ค่อนข้างเป็นกลาง (Wikipedia) จะเห็นว่าที่กระบวนการผลิตระดับ 14 นาโนเมตร ความหนาแน่นของทรานซิสเตอร์ฝั่งอินเทลเยอะที่สุด (37.5 ล้านตัวต่อตารางมิลลิเมตร) ใกล้เคียงกับตัวเลขของ GlobalFoundries ในขณะที่ตัวเลขของ TSMC น้อยกว่าพอสมควร (28.8 ล้านตัว)

พอลดขนาดลงมาเหลือ 10 นาโนเมตร (GlobalFoundries เริ่มลงทุนไม่ไหวแล้ว โลกเหลือแค่ 3 ราย) จะเห็นว่าตัวเลขของฝั่ง TSMC และซัมซุงค่อนข้างใกล้เคียงกัน แต่อินเทลกระโดดไปไกลถึงระดับ 100 ล้านตัวต่อตารางมิลลิเมตร หรือมากกว่ากันเกือบ 2 เท่า - Wikipedia

ฝ่ายที่เสียประโยชน์จาก "การตลาดนาโนเมตร" อย่างอินเทลย่อมออกมาแก้ความเข้าใจผิดนี้ ในปี 2017 (นับเป็นเวลาสองปี หลังจาก 10 นาโนเมตรผิดแผน) อินเทลออกโพสต์ที่ชื่อว่า Let’s Clear Up the Node Naming Mess เสนอให้ใช้การวัดความหนาแน่นทรานซิสเตอร์เป็นมาตรฐานของวงการ แทนการระบุเลขนาโนเมตร (ซึ่งแน่นอนว่าข้อเรียกร้องของอินเทลไม่เป็นผล)

จากกราฟจะเห็นว่าความหนาแน่นของทรานซิสเตอร์ในยุค 10nm ของอินเทล เพิ่มขึ้นจาก 14 นาโนเมตรแบบก้าวกระโดดมาก และนี่คือเหตุผลว่าทำไมอินเทลไป 10 นาโนเมตรไม่สำเร็จสักที เพราะเป็นการตั้งเป้าที่สูงเกินไปมากนั่นเอง

เท่านั้นยังไม่พอ หากเราดูการผลิตระดับ 7 นาโนเมตรในปัจจุบัน จะเห็นว่าตัวเลขความหนาแน่นของ TSMC หรือซัมซุง ยังน้อยกว่า 10 นาโนเมตรของอินเทลด้วยซ้ำ

นั่นแปลว่าถ้าพิจารณาจากตัวเลขความหนาแน่นของทรานซิสเตอร์เพียงอย่างเดียว สิ่งที่อินเทลพยายามทำกับ 10 นาโนเมตรในปี 2016 ก็เทียบได้กับ TSMC ทำ 7 นาโนเมตร ในช่วงปี 2018

ภาพจาก Wikichip

10 นาโนเมตร ผู้มาก่อนกาล

ทั้งหมดที่กล่าวมาเพื่อชี้ให้เห็นว่า อินเทลในปี 2016 นำหน้า TSMC อยู่พอสมควร แต่เลือกจะ "ก้าวกระโดดครั้งใหญ่" ด้วย 10 นาโนเมตรที่มีความหนาแน่นของทรานซิสเตอร์สูงมาก

ในขณะที่ TSMC และซัมซุงเลือกแนวทางค่อยๆ เดิน ใช้วิธีเดินมาทีละก้าว จนมาถึง 7 นาโนเมตรที่เทียบได้กับ 10 นาโนเมตรของอินเทล มาถึงวันนี้ก็พิสูจน์ชัดแล้วว่าวิธีการของ TSMC และซัมซุงถูกต้องเหมาะสมกว่า

แต่บริษัทระดับอินเทลพลาดกันง่ายๆ อย่างนี้เลยหรือ

นอกจากปัจจัยเรื่องการตั้งเป้าทรานซิสเตอร์หนาแน่น 100 ล้านตัวที่ "ทะลุเพดาน" ไปมากแล้ว ผมคิดว่าอีกปัจจัยหนึ่งที่ส่งผลให้แผน 10 นาโนเมตรของอินเทลผิดพลาด คือตัวเทคโนโลยีการผลิตเอง

ในโลกของทรานซิสเตอร์ที่มีขนาดเล็กลงเรื่อยๆ ปัญหาเรื่องความแม่นยำ (accuracy) ของการผลิตขาของทรานซิสเตอร์ย่อมยากขึ้นเรื่อยๆ จนในปัจจุบันต้องใช้เทคนิคการพิมพ์ (lithography) ตัวแผ่นวงจรด้วยแสง-รังสี หรือที่เรียกว่า photolithography กันแล้ว (เพราะไม่มีเครื่องมืออื่นที่เล็กขนาดนั้นแล้ว)

ภาพจาก Intel

เทคนิคสำคัญที่ใช้ในยุค 7 นาโนเมตรคือ extreme ultraviolet lithography (EUV หรือ EUVL) เป็นการใช้รังสีอัลตร้าไวโอเล็ตความเข้มข้นสูงกว่าปกติมาก ความยาวคลื่น 13.5 นาโนเมตร เกือบเท่ารังสี X-ray แล้ว (ก่อนยุค EUV เป็นยุคของ DUV หรือ deep ultraviolet)

เทคนิค EUVL มีข้อจำกัดสูง มีความซับซ้อนสูง ต้องอยู่ในสภาพสุญญากาศ ต้องใช้พลังงานมาก และที่สำคัญมีราคาแพงมาก!

บริษัทที่เป็นแกนกลางของโลกเซมิคอนดักเตอร์ยุคใหม่คือ ASML จากเนเธอร์แลนด์ ที่สร้างเครื่องยิง EUVL มาขายให้เหล่าโรงงานผลิตชิปอีกทีหนึ่ง ไม่ว่าจะเป็นอินเทล, TSMC, ซัมซุง ล้วนแต่ใช้เครื่องของ ASML ด้วยกันทั้งสิ้น

เครื่อง EUVL ของ ASML มีราคาแพงถึงระดับเครื่องละ 100 ล้านดอลลาร์ และ ASML มีกำลังการผลิตเครื่องได้จำนวนจำกัดในแต่ละปีด้วย (ปัจจุบันมีเครื่อง EUVL เพียงแค่หลักไม่กี่สิบเครื่องในโลก) เรียกได้ว่าแพง แถมต่อให้มีเงินก็ซื้อไม่ได้ง่ายๆ อีกด้วย

หน้าตาเครื่อง EUVL รุ่นล่าสุดของ ASML

บริษัทอย่างอินเทลมองข้ามเทคโนโลยี EUVL หรือไม่? ก็ไม่ใช่แบบนั้นอีก เพราะในปี 2012 ทั้งสามบริษัทต่างเข้ามาลงทุนใน ASML เพื่อช่วยพัฒนาเทคโนโลยี EUVL เพื่ออนาคตภายภาคหน้า โดยอินเทลเคยเข้าไปลงทุนเป็นเงิน 4 พันล้านดอลลาร์ ซื้อหุ้น 10% ใน ASML ด้วย - EE Times

เมื่อเทคโนโลยี EUVL เริ่มเดินหน้าได้ ทั้งสามบริษัทก็ลดจำนวนหุ้นของตัวเองใน ASML ลง และลดความสัมพันธ์จากการเป็นเจ้าของ มาเป็นคู่ค้าเพียงอย่างเดียว

ถ้าอินเทลรู้จัก EUVL มาตั้งแต่แรก ทำไมอินเทลไม่ใช้ EUVL คำตอบคือเรื่องของช่วงเวลา

ในตอนที่อินเทลอยากไป 10 นาโนเมตรในปี 2015-2016 เทคโนโลยี EUVL ยังไม่พร้อม ทำให้อินเทลเลือกเดินหน้าต่อด้วยเทคโนโลยีเดิม (multi-patterning) ไปก่อน บนเว็บไซต์อินเทลยังมีโพสต์ถึง EUVL ในปี 2016 ที่บอกว่าเป็นการเดินทางระยะไกล

เทคนิคของอินเทลเรียกว่า Hyper Scaling มันคือการยัดทรานซิสเตอร์จำนวน 2.7 เท่าจากเดิมลงในพื้นที่เดิม เมื่อเทียบกับการผลิตระดับ 14 นาโนเมตร

แต่เมื่อแผน Hyper Scaling ของอินเทลทะเยอทะยานเกินไป จนการผลิตระดับ 10 นาโนเมตรเกิดปัญหาขึ้นมา ในโลกของเซมิคอนดักเตอร์ที่การลงทุนสร้างโรงงานมีราคาแพงมากๆ การที่อินเทลจะสร้างโรงงานใหม่ เปลี่ยนวิธีการผลิตใหม่ ก็คงไม่ง่ายนัก ได้แต่ต้องเดินหน้าต่อไปด้วยเทคโนโลยีเดิม เพราะลงทุนไปมากแล้ว

ในขณะที่ TSMC และซัมซุงตามมาทีหลัง ด้วยแผนการที่ไม่ทะเยอทะยานเท่ากับอินเทลในตอน 10 นาโนเมตร และเมื่อโลกเข้าสู่ระดับ 7 นาโนเมตรอย่างรวดเร็ว (ด้วยปัจจัยเรื่องตลาดเกิดใหม่ ทั้งจีพียูและมือถือ ที่เป็นลูกค้าของ TSMC/ซัมซุง ช่วยให้มีกำลังเงินขยายโรงงานได้รวดเร็วขึ้นมาก) เทคโนโลยี EUVL ก็มีความพร้อมแล้ว

หมายเหตุ: ปัจจุบัน อินเทลมี EUVL แล้ว แถมยังเคยเปิดให้ Engadget เข้ามาดูโรงงานที่มี EUVL ในปี 2020 ตามคลิปด้านล่าง แต่ความพร้อมในระดับผลิตจำนวนมากมีแค่ไหนก็เป็นสิ่งที่ต้องตั้งคำถามต่อไป

บทสรุป: การต่อสู้กันของสองโมเดลการผลิต

ทั้งหมดที่กล่าวมาจึงเป็นคำอธิบายว่าทำไมอินเทลถึงไม่สามารถก้าวข้ามจาก 14 นาโนเมตรได้สักที คำตอบคือเกิดจากปัจจัยหลายอย่างผสมกัน ทั้งมาก่อนกาล ทั้งทะเยอทะยานเกินไป ทั้งโมเดลการผลิตแบบ IDM ที่ปรับเปลี่ยนตัวเองได้ช้ากว่า พอพลาดแล้วเลยกลับตัวลำบาก

ในทางกลับกัน บริษัทรับจ้างผลิตแบบ TSMC เกิดจากปัจจัยเรื่องชิปประเภทใหม่ๆ (จีพียู/มือถือ), ความสัมพันธ์กับบริษัท fabless ที่เปิดให้ทุกคนเติบโตได้, และการขยับขยายโรงงานผลิตแบบค่อยเป็นค่อยไป ไม่ก้าวกระโดดแบบอินเทล

เมื่อกระบวนการผลิตของอินเทล ผูกกับแผนการออกซีพียูใหม่อย่างแนบแน่น (ตามโมเดล Tick-Tock ที่กล่าวไปในตอนที่แล้ว) การออกซีพียูใหม่ที่เป็นหัวใจสำคัญของบริษัทจึงติดขัดตามไปด้วย

เรียกได้ว่า อินเทลมาพลาดเอาจุดที่เป็นแกนกลางสำคัญของทุกสิ่ง พอพลาดแล้วก็เลยสะเทือนไปทั้งบริษัทเลยทีเดียว

แต่นี่ยังเป็นเพียงแค่ปัญหาข้อเดียวของอินเทลในรอบ 10 ปีให้หลังเท่านั้น

อินเทลยังมีปัญหาอื่นๆ อีกมากมาย ไม่ว่าจะเป็นการตกขบวนจีพียู การพลาดโอกาสของชิปมือถือ รวมถึงปัจจัยด้านการบริหาร ค่านิยมในองค์กร ฯลฯ แม้กระทั่งปัญหาซีอีโอต้องลาออกเพราะผู้หญิง ซึ่งเราจะกล่าวถึงประเด็นเหล่านี้กันใน ตอนที่สาม

หมายเหตุ: เราอาจเปรียบเทียบว่าเป็นการต่อสู้กันของโมเดล 3 แบบคือ pure-play (TSMC), IDM แบบดั้งเดิม (อินเทล), IDM แบบเปิดรับลูกค้าภายนอก (ซัมซุง) ส่วนกรณีของ GlobalFoundries ถือเป็นเบอร์สองของ pure-play แต่ก็หลุดสมการไปแล้วเพราะลงทุน 7 นาโนเมตรไม่ไหว แสดงให้เห็นว่าวงการนี้แข่งขันสูง และมีราคาแพงแค่ไหน

บทความนี้เน้นไปที่การต่อสู้กันของ 2 โมเดลที่สุดปลายคือ TSMC และอินเทลเป็นสำคัญ ส่วนกรณีของซัมซุงที่เป็น IDM แบบลูกผสมนั้นถือเป็นกรณีค่อนข้างเฉพาะ และซัมซุงเองก็มีธุรกิจอื่นอีกจำนวนมากที่เป็นปัจจัยผันแปรด้วย (เช่น นำกำไรจากธุรกิจอื่นมาสนับสนุนธุรกิจเซมิคอนดักเตอร์) ทำให้การวิเคราะห์ธุรกิจเซมิคอนดักเตอร์ของซัมซุงโดยตรงทำได้ยาก

หมายเหตุ 2: สำหรับผู้ที่สนใจปัญหา 10 นาโนเมตรของอินเทล บทความที่ให้รายละเอียดได้ดีมากคือ EE Times ที่มี 2 ตอน ตอนที่ 1 ตอนที่ 2