อินเทลเปิดแผนเทคโนโลยีแพ็กเกจชิป ระยะห่างขาต่ำกว่า 10 ไมครอนภายในปี 2023

ในงาน Intel Accelerate วันนี้นอกจากการประกาศแผนเทคโนโลยีการผลิตชิปแล้ว อินเทลยังประกาศแผนแพ็กเกจแยกจากกัน โดยวางแผนการลดระยะห่างระหว่างขา (bump pitch) ให้ลดลงไปจนถึงระดับต่ำกว่า 10 ไมครอนภายในปี 2023 (ไมครอนคือ 1 ใน 1000 ของมิลลิเมตร) โดยเทคโนโลยีที่อยู่ในแผนได้แก่

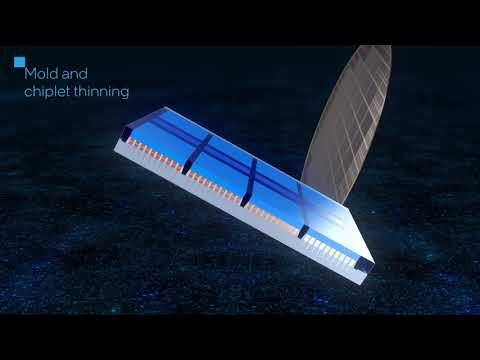

- EMIB (embedded multi-die interconnect bridge) เทคโนโลยีแพ็กเกจตั้งแต่ปี 2017 แต่ในชิปเซิร์ฟเวอร์ Sapphire Rapids จะใช้ EMIB รุ่นต่อไป ที่ลดระยะห่างระหว่างขาจาก 55 ไมครอนเหลือ 45 ไมครอน

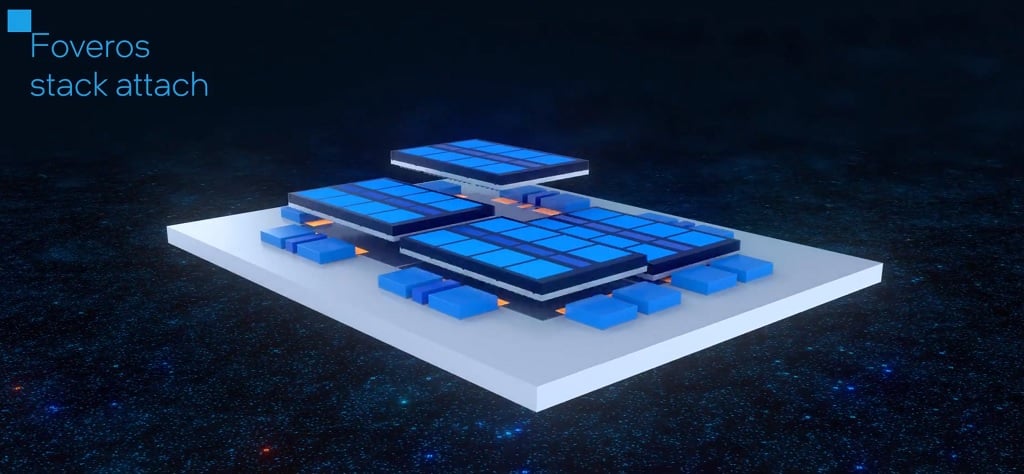

- Foveros อินเทลระบุว่าจะมีแนวทางการเรียงชิปแบบ 3 มิติแบบใหม่ และลดระยะห่างระหว่างขาเหลือ 36 ไมครอน ซีพียูสำหรับไคลเอนต์ Meteor Lake จะใช้เทคโนโลยีนี้

- Foveros Omni เทคโนโลยีเชื่อมชิปในแพ็กเกจได้อิสระขึ้น โดยชิปด้านบนสามารถเชื่อมกับชิปด้านล่างได้หลายชิป รวมถึงสามารถเชื่อมกับชิปที่เทคโนโลยีการผลิตต่างกัน คาดว่าจะเริ่มผลิตได้จริงในปี 2023

- Foveros Direct เชื่อมระหว่างชิปโดยมีความต้านทานต่ำจนแทบทำงานได้เหมือนเป็นชิปเดียวกัน ระยะห่างระหว่างขาเหลือต่ำกว่า 10 ไมครอน คาดว่าจะพร้อมใช้งานในปี 2023 เช่นกัน

ในการแถลงข่าวครั้งนี้มี AWS ประกาศว่าจะใช้เทคโนโลยีแพ็กเกจของอินเทลเป็นรายแรก โดยไม่ได้ระบุชัดเจนว่าใช้เทคโนโลยีใด

ที่มา - Intel

Blognone Jobs Premium