อินเทลเปิดตัว Xeon "Sapphire Rapids" ใช้สถาปัตยกรรมแยกส่วน เพิ่ม AMX ประมวลผลเมทริกซ์

นอกจากซีพียู Alder Lake และจีพียู Intel Arc ที่มี XeSS อินเทลยังเปิดข้อมูลของผลิตภัณฑ์ฝั่งเซิร์ฟเวอร์ ได้แก่ซีพียู Xeon Scalable รุ่นถัดไป "Sapphire Rapids" และจีพียูศูนย์ข้อมูล "Ponte Vecchio" เพิ่มเติมด้วย

โพสต์นี้เอาเฉพาะ Sapphire Rapids อย่างเดียวก่อนนะครับ

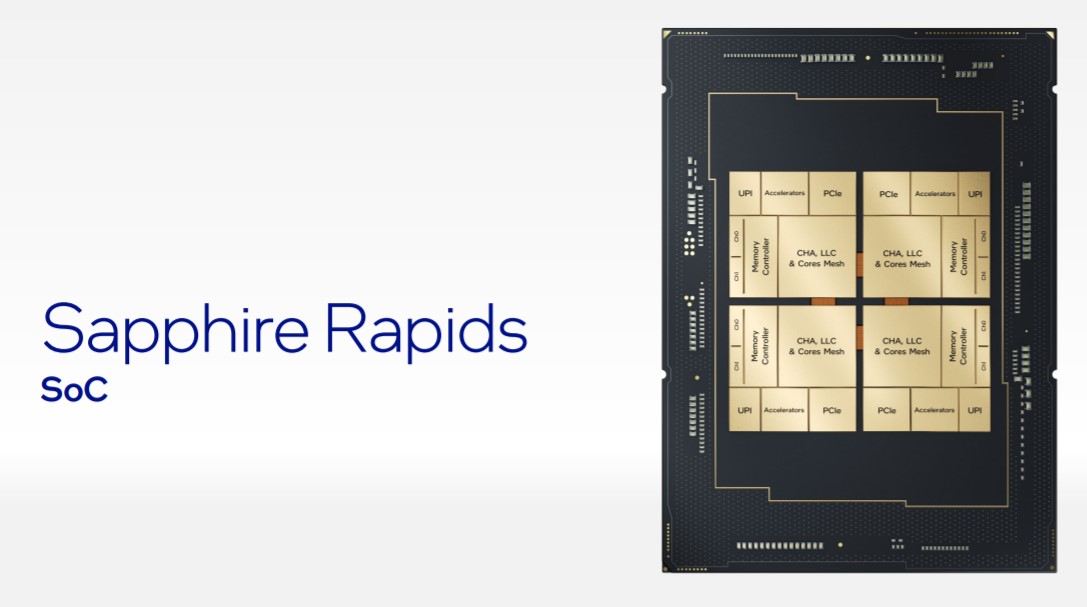

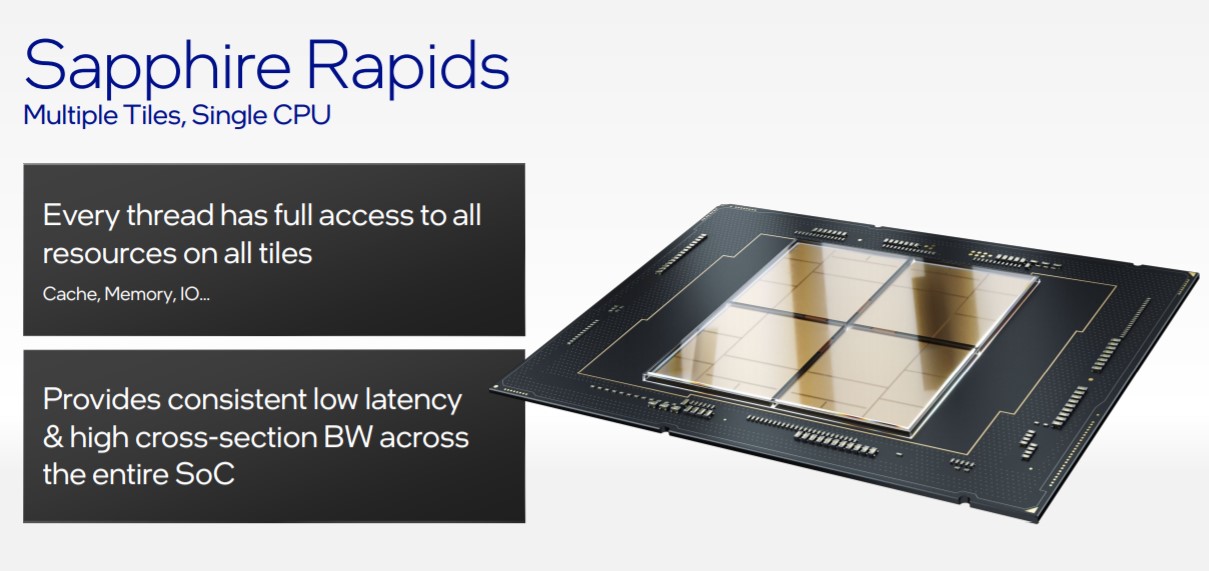

การเปลี่ยนแปลงสำคัญที่สุดของ Xeon "Sapphire Rapids" คือเปลี่ยนมาใช้สถาปัตยกรรมแบบ modular ที่อินเทลเรียกว่า multi-tile design หรือการแบ่งชิปย่อย (tile) แล้วนำมาวางต่อกันผ่านบัส interconnect แทนผลิตชิปทั้งหมดลงบนแผ่น die แผ่นเดียว (ลักษณะเดียวกับที่ AMD Zen ใช้มาสักระยะหนึ่งแล้ว เท่ากับว่าสุดท้ายอินเทลก็ต้องยอมเดินตาม AMD)

ความแตกต่างคืออินเทลให้แพ็กเกจแบบวางตั้งที่เรียกว่า Embedded Multi-die Interconnect Bridge (EMIB) ซึ่งใช้กับหน่วยประมวลผลตัวอื่นๆ อย่าง Ponte Vecchio ด้วย

ในภาพที่อินเทลนำมาให้ดู Sapphire Rapids ประกอบด้วย 4 tiles ซึ่งแต่ละ tile มีทั้งหน่วยประมวลผลหลัก, ตัวช่วยเร่งการประมวลผล (accelerator), ตัวควบคุมหน่วยความจำและ I/O แยกของตัวเอง

หน่วยประมวลผลหลักของ Sapphire Rapids ใช้แกน Performance Core "Golden Cove" ตัวเดียวกับใน Alder Lake แต่เป็นเวอร์ชันใหญ่สำหรับงานศูนย์ข้อมูล

ของใหม่ที่สำคัญในแกน Golden Cove เวอร์ชันศูนย์ข้อมูล คือ หน่วยประมวลผลเมทริกซ์ (ข้อมูล 2 มิติ) ชื่อว่า Advanced Matrix Extensions (AMX) โดยเป็นฮาร์ดแวร์เร่งการประมวลผลแยกจากแกนซีพียูหลัก (ตอนนี้ยังมีเฉพาะใน Sapphire Rapids ไม่ได้มีบน Alder Lake)

AMX เป็นการขยายให้ซีพียูสามารถคำนวณเมทริกซ์ได้เยอะขึ้นในรอบสัญญาณเดียว (คำนวณเลขจำนวนเต็ม int8 ได้พร้อมกัน 2048 ชุด) เพิ่มขึ้น 8 เท่าจากชุดคำสั่งเดิม

วิธีการทำงานของ AMX คือโหลดข้อมูลจากแกนซีพียูหลัก มาใส่ TILES ก่อนแล้วนำไปคำนวณด้วย TMUL อีกทีหนึ่ง

อินเทลบอกว่าสร้าง AMX ขึ้นมารองรับโหลดงานประเภทใหม่ๆ คืองานสาย AI ที่ต้องประมวลผลเมทริกซ์เยอะๆ โดยตัวเลขของอินเทลเปรียบเทียบระหว่างชุดคำสั่ง AVX-512 ของเดิม (เวกเตอร์) และ AMX ของใหม่ (เมทริกซ์) จะเห็นว่า AMX สามารถประมวลผลต่อรอบสัญญาณได้เยอะกว่ามาก (8 เท่าถ้าเป็นข้อมูลแบบ INT8)

Sapphire Rapids จะมีทั้ง AVX-512 และ AMX มาให้ในตัว แต่ถ้าดูจากทิศทาง Alder Lake ปิดการทำงานของ AVX-512 ก็น่าสนใจถึงชะตากรรมของ AVX-512 ในระยะยาว

คลิปสาธิตการทำงานของ AMX ใน Sapphire Rapids

ของใหม่อีกอย่างใน Performance Core คือ Data Streaming Accelerator (DSA) เป็นการโยกงานพื้นฐาน อย่างการย้ายตำแหน่งของข้อมูล (data movement) จากแกนซีพียูหลักไปยังหน่วยประมวลผลรอง (อินเทลใช้คำว่า Acceleration Engines) ช่วยลดโหลดงานของแกนซีพียูหลักลง

การโยกงานจากแกนซีพียูหลักไปยัง AMX และ DSA จะผ่านตัวกระจายงาน (dispatch) ที่อินเทลเรียกว่า Accelerator Interfacing Architecture (AIA)

ของใหม่นอกแกนซีพียูหลัก ได้แก่ การรองรับแรม HBM (High-Bandwidth Memory) ที่ฝั่ง AMD รองรับมานานแล้ว, บัส Compute eXpress Link (CXL) 1.1, Ultra Path Interconnect (UPI) 2.0, PCIe 5.0

Sapphire Rapids จะผลิตโดยโรงงานของอินเทลเอง ใช้กระบวนการผลิต Intel 7 (10 นาโนเมตร) ตัวเดียวกับ Alder Lake กำหนดการวางจำหน่ายแบบคร่าวๆ คือในปี 2022

สรุปของใหม่ใน Sapphire Rapids

ที่มา - Intel